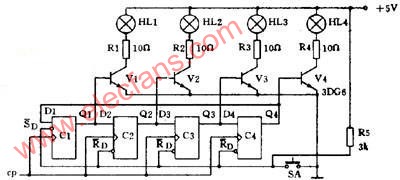

在數(shù)字電路中,凡是任一時(shí)刻的穩(wěn)定輸出不僅決定于該時(shí)刻的輸入,而且還和電路原來狀態(tài)有關(guān)者都叫時(shí)序邏輯電路。時(shí)序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時(shí)序邏輯電路的狀態(tài)是靠具有存儲(chǔ)功能的觸發(fā)器所組成的存儲(chǔ)電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

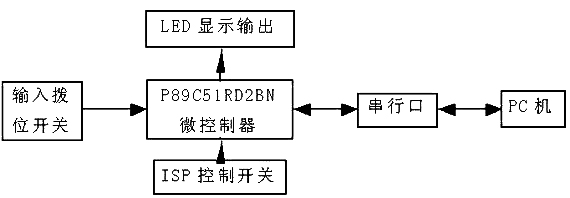

作者: 小魚,Xilinx學(xué)術(shù)合作 一. 概述 時(shí)序邏輯示意圖,如下圖所示。數(shù)據(jù)從一個(gè)寄存器出來,經(jīng)過組合邏輯到達(dá)下一個(gè)寄存器。 在學(xué)習(xí)數(shù)字電路的過程中,我們都知道時(shí)序邏輯,但是大家對時(shí)序邏輯真的

2020-12-25 14:39:28 4147

4147

;nbsp; 組合邏輯電路設(shè)計(jì)中應(yīng)注意的問題 3.2 算術(shù)運(yùn)算電路 3.2.1 半加器電路

2008-05-15 21:57:28

電子工程師必備專業(yè)書,文件比較大,給點(diǎn)耐心。附件數(shù)字邏輯電路的ASIC設(shè)計(jì).pdf13.5 MB

2018-12-04 09:01:06

數(shù)字電子電路技術(shù)--時(shí)序邏輯電路

2017-05-01 21:23:36

數(shù)字電子電路技術(shù)--組合邏輯電路[hide][/hide]

2017-05-01 21:32:09

數(shù)字電子技術(shù)-- 時(shí)序邏輯電路[hide][/hide]

2017-05-01 21:51:53

數(shù)字電子技術(shù)-- 組合邏輯電路[hide][/hide]

2017-05-01 22:20:58

化簡→畫邏輯電路圖。時(shí)序電路設(shè)計(jì):列原始狀態(tài)轉(zhuǎn)移圖和表→狀態(tài)優(yōu)化→狀態(tài)分配→觸發(fā)器選型→求解方程式→畫邏輯電路圖。在實(shí)際應(yīng)用中,數(shù)字電路設(shè)計(jì)的基本思路是先選擇標(biāo)準(zhǔn)的通用集成電路,然后,再利用這些芯片

2019-02-27 11:55:00

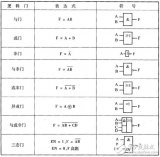

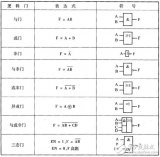

邏輯電路主要邏輯門電路之間的關(guān)系是怎樣的

2020-04-15 17:53:30

邏輯電路的糾錯(cuò)技術(shù)是如何實(shí)現(xiàn)的?糾錯(cuò)技術(shù)在邏輯電路中有什么作用?

2021-06-18 09:50:31

FPGA則應(yīng)該理解為可用電腦編輯的數(shù)字邏輯電路集成芯片,其實(shí)是在描繪一個(gè)數(shù)字邏輯電路。關(guān)于兩者的區(qū)別在于以下:1、速度上(兩者最大的差別)因?yàn)镕PGA是硬件電路,運(yùn)行速度則取決于晶振速度,系統(tǒng)

2021-07-13 08:43:08

Multisim在數(shù)字邏輯電路中的應(yīng)用8.1數(shù)字邏輯電路的創(chuàng)建8.2全加器及其應(yīng)用8.3譯碼器及其應(yīng)用8.4數(shù)據(jù)選擇器及其應(yīng)用8.5組合邏輯電路的冒險(xiǎn)現(xiàn)象8.6觸發(fā)器8.7同步時(shí)序電路分析

2012-07-18 21:47:03

VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì).侯伯亭&顧新

2020-05-11 09:22:18

VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì).侯伯亭&顧新.掃描版

2020-05-03 09:46:42

[VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì)].侯伯亭&顧新.掃描版

2020-05-21 09:25:46

四路2輸入CMOS邏輯或門CD4071四路2輸入CD4075三路3輸入CD4072雙4輸入7432四路2輸入邏輯或門在下一本關(guān)于數(shù)字邏輯門的教程中,我們將介紹TTL和CMOS邏輯電路中使用的數(shù)字邏輯NOT門功能,以及其布爾代數(shù)定義和真值表。

2021-01-21 08:00:00

`內(nèi)容簡介本書是“實(shí)用電子電路設(shè)計(jì)叢書”之一。本書以實(shí)現(xiàn)高速高可靠性的數(shù)字系統(tǒng)設(shè)計(jì)為目標(biāo),以完全同步式電路為基礎(chǔ),從技術(shù)實(shí)現(xiàn)的角度介紹ASIC邏輯電路設(shè)計(jì)技術(shù)。內(nèi)容包括:邏輯門電路、邏輯壓縮、組合

2018-04-03 17:14:16

FPGA數(shù)字邏輯電路的設(shè)計(jì)與分析,包含項(xiàng)目實(shí)例、全流程設(shè)計(jì)說明文檔,項(xiàng)目源代碼文件。

2021-03-30 14:48:05

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

華為 邏輯電路設(shè)計(jì)規(guī)范自己選擇下載閱讀!

2015-08-04 14:46:14

1、如何點(diǎn)亮LED燈實(shí)現(xiàn)流水燈點(diǎn)亮LED_狀態(tài)機(jī)在之前的文章中,我們已經(jīng)提到過數(shù)字邏輯電路分為組合邏輯電路和時(shí)序邏輯電路,并對組合邏輯電路的模塊化設(shè)計(jì)進(jìn)行了介紹。從這篇文章開始,我們開始介紹分享一些

2022-07-22 15:25:03

Verilog程序模塊的結(jié)構(gòu)是由哪些部分組成的?如何去實(shí)現(xiàn)時(shí)序邏輯電路和組合邏輯電路的設(shè)計(jì)呢?

2021-11-03 06:35:57

“ 1”。結(jié)果是組合邏輯電路沒有反饋,并且施加到其輸入的信號(hào)的任何變化都會(huì)立即對輸出產(chǎn)生影響。換句話說,在組合邏輯電路中,輸出始終取決于其輸入的組合。因此,組合電路是無記憶的。因此,如果其輸入條件之一從

2021-01-19 09:29:30

、可編程器件設(shè)計(jì)時(shí)序邏輯電路的特點(diǎn)、方法;3 掌握時(shí)序邏輯電路的調(diào)試方法;4 進(jìn)一步提高排除數(shù)字電路故障的能力。

2009-03-19 15:10:18

時(shí)序邏輯電路設(shè)計(jì)6.1 基本D觸發(fā)器的設(shè)計(jì)6.2 JK觸發(fā)器6.3 帶異步復(fù)位/置位端的使能T觸發(fā)器6.4 基本計(jì)數(shù)器的設(shè)計(jì)6.5 同步清零的計(jì)數(shù)器6.6 同步清零的可逆計(jì)數(shù)器6.7 同步預(yù)置數(shù)的計(jì)數(shù)器

2009-03-20 10:04:53

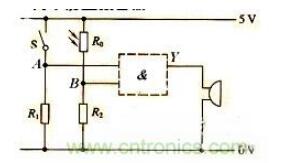

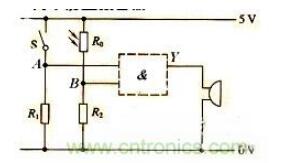

,是一些什么樣的電路如此“神通廣大”呢?——邏輯電路。處理數(shù)字信號(hào)的電路叫數(shù)字電路,數(shù)字電路主要研究電路的邏輯功能。下面我們簡單介紹幾種簡單又有趣的電路在生活中的應(yīng)用。1.簡單防盜報(bào)警器在工廠、銀行等

2018-07-12 13:03:30

;nbsp; 在數(shù)字電路中,數(shù)字電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類。組合邏輯電路:任何時(shí)刻的輸出取決于這一

2009-09-16 16:05:29

組合邏輯電路是無記憶數(shù)字邏輯電路,其任何時(shí)刻的輸出僅取決于其輸入的組合。 與順序邏輯電路不同,順序邏輯電路的輸出取決于它們的當(dāng)前輸入和先前的輸出狀態(tài),從而給它們提供某種形式的存儲(chǔ)器。組合

2020-12-31 17:01:17

在多年的數(shù)字邏輯電路的教學(xué)中,發(fā)現(xiàn)高職院校的學(xué)生在邏輯電路的入門學(xué)習(xí)中理解邏輯代數(shù)中的各種邏輯運(yùn)算的含義及將各種邏輯運(yùn)算與實(shí)際邏輯電路的聯(lián)系起來比較困難,導(dǎo)致對邏輯代數(shù)運(yùn)算定律和定理理解難,進(jìn)而給

2010-05-13 09:11:16

多輸入時(shí)序電路的基本原理是什么?基于數(shù)據(jù)選擇器和D觸發(fā)器的多輸入時(shí)序邏輯電路設(shè)計(jì)

2021-04-29 07:04:38

組合邏輯電路的基本模塊是什么?時(shí)序邏輯電路怎樣進(jìn)行工作的?

2021-09-18 09:19:42

集成邏輯電路、組合邏輯電路實(shí)驗(yàn)?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)方法

2008-12-11 23:36:32

數(shù)字邏輯電路的內(nèi)容:數(shù)制與編碼,,邏輯代數(shù)和邏輯函數(shù),集成邏輯門,組合邏輯電路,中規(guī)模集成組

2008-09-06 01:54:26 33

33 基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設(shè)計(jì)一、實(shí)驗(yàn)?zāi)康?. 熟悉組合邏輯電路的基本設(shè)計(jì)方法;2. 練習(xí)用門電路、譯碼器、數(shù)據(jù)選擇器設(shè)計(jì)組合邏輯電路。二、實(shí)驗(yàn)設(shè)備1.

2008-09-12 16:41:23 0

0 時(shí)序邏輯電路的輸出不但和當(dāng)前輸入有關(guān),還與系統(tǒng)的原先狀態(tài)有關(guān),即時(shí)序電路的當(dāng)前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達(dá)到這一目的,時(shí)序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

71 組合邏輯電路電子教案:數(shù)字邏輯電路可分為兩大類: 一類叫組合邏輯電路;另一類叫時(shí)序邏輯電路。本章首先介紹組合邏輯電路的共同特點(diǎn)和描述方法,然后重點(diǎn)介紹組合邏輯電

2009-09-01 08:58:29 0

0 數(shù)字系統(tǒng)的基本算法與邏輯電路實(shí)現(xiàn):本章主要介紹數(shù)字系統(tǒng)的基本算法設(shè)計(jì)及對應(yīng)的邏輯電路的實(shí)現(xiàn)方法。算法設(shè)計(jì)中主要考慮的因素1.邏輯指標(biāo)這是數(shù)字系統(tǒng)最重要、

2009-09-01 09:04:09 0

0 異步時(shí)序邏輯電路:本章主要從同步時(shí)序邏輯電路與異步時(shí)序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時(shí)序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 0

0 用Protel 99實(shí)現(xiàn)邏輯電路設(shè)計(jì):介紹可鳊程邏輯器件(PLD)應(yīng)用和相應(yīng)軟件的發(fā)展;使用EDA 工具Protel 99的PLD設(shè)計(jì)簡單邏輯電路的一般方法。關(guān)鍵詞Protel 99 PLD CUPL語言

眾所周知,

2009-11-01 10:13:34 0

0 VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì):本書系統(tǒng)地介紹了一種硬件描述語言,即VHDL語言設(shè)計(jì)數(shù)字邏輯電路和數(shù)字系統(tǒng)的新方法。這是電子電路設(shè)計(jì)方法上一次革命性的變化,也是邁

2010-02-06 16:55:22 359

359 摘要:本文對數(shù)字邏輯電路關(guān)于同步時(shí)序邏輯電路設(shè)計(jì)的關(guān)鍵步驟中,引入代數(shù)理論輔助設(shè)計(jì)作了一些探討,并用實(shí)例表明這樣的努力使設(shè)計(jì)過程得到了大大的簡化。關(guān)鍵詞:同

2010-04-29 09:35:20 12

12 摘要:介紹了可以簡化邏輯電路設(shè)計(jì)的可蝙程邏輯器件EPLD.詳述了它的工作原理、開發(fā)工具舉例說明了應(yīng)用IPLD設(shè)計(jì)電路的具體過程。

2010-04-30 10:21:03 35

35 講述組合邏輯電路設(shè)計(jì)基礎(chǔ)

2010-05-06 10:29:15 0

0 數(shù)字邏輯電路設(shè)計(jì)課程

數(shù)字邏輯電路的設(shè)計(jì)包括兩個(gè)方面:基本邏輯功能電路設(shè)計(jì)和邏輯電路系統(tǒng)設(shè)計(jì)。關(guān)于基本邏輯功能電路設(shè)計(jì)一般在《數(shù)字電路技術(shù)基礎(chǔ)

2010-05-24 16:05:50 0

0 現(xiàn)代數(shù)字邏輯電路實(shí)踐教學(xué)探索與改革

摘要:可編程邏輯器件的出現(xiàn)使數(shù)字電路設(shè)計(jì)方式發(fā)生了革命性變化,設(shè)計(jì)者采用EDA軟件

2010-05-24 17:22:24 19

19 數(shù)字邏輯電路按邏輯功能和電路組成的特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數(shù)字邏輯電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類。組合邏輯電路在任一時(shí)刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過去的輸入無關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數(shù)字集成電路,根據(jù)原理可分為兩大類,既組合邏輯電路和時(shí)序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態(tài)僅由同一時(shí)刻的輸入狀態(tài)決定,與電路的原

2010-08-18 15:05:23 55

55 數(shù)字邏輯電路

數(shù)字邏輯電路的用途和特點(diǎn)

數(shù)字電子電路中的后起之秀是數(shù)字邏輯電路。把它叫做數(shù)字電路是因?yàn)?b class="flag-6" style="color: red">電路中傳遞的雖然也是脈沖,但這些脈沖是

2009-11-10 10:13:26 17158

17158 各種邏輯電路簡介

邏輯電路:

以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字信號(hào)邏輯運(yùn)算和操作的電路。分組合邏輯電路和

2009-11-24 13:27:04 2959

2959 如何看懂數(shù)字邏輯電路

數(shù)字電子電路中的后起之秀是數(shù)字邏輯電路。把它叫做數(shù)字電路是因?yàn)?b class="flag-6" style="color: red">電路中傳遞的雖然也是脈沖,但這些脈沖是用來表示二進(jìn)制數(shù)碼的,例如

2010-05-24 11:35:01 2727

2727

數(shù)字邏輯電路教學(xué)中的C語言描述和應(yīng)用

摘要:為了改進(jìn)數(shù)字邏輯電路教學(xué)方法以適應(yīng)電子技術(shù)迅猛發(fā)展的需要,我們探索和實(shí)踐了數(shù)字邏輯電路教

2010-05-24 15:40:52 1839

1839

為縮短理論與實(shí)踐的距離,提高靈活應(yīng)用數(shù)字元器件的能力,提出了組合邏輯電路設(shè)計(jì)的第五步。組合邏輯電路設(shè)計(jì)通常有四步,設(shè)計(jì)完成畫出符合功能要求的邏輯圖,一般是把其轉(zhuǎn)換

2011-05-03 17:58:26 61

61 電子發(fā)燒友網(wǎng)站提供《[VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計(jì)].侯伯亭&顧新.掃描版.txt》資料免費(fèi)下載

2012-07-10 18:32:33 0

0 電子發(fā)燒友網(wǎng)站提供《[數(shù)字邏輯電路].劉必虎&沈建國.掃描版.txt》資料免費(fèi)下載

2012-10-01 11:06:10 0

0 電子發(fā)燒友網(wǎng)站提供《[數(shù)字邏輯電路].劉必虎&沈建國.掃描版.txt》資料免費(fèi)下載

2012-10-01 18:59:11 0

0 電子發(fā)燒友網(wǎng)站提供《經(jīng)典教材-VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì)(第三版).txt》資料免費(fèi)下載

2014-08-27 11:41:09 0

0 數(shù)字邏輯電路設(shè)計(jì)實(shí)踐_電工電子實(shí)驗(yàn)中心實(shí)驗(yàn)報(bào)告。

2015-10-29 16:25:13 0

0 數(shù)字邏輯電路分析與設(shè)計(jì)_Digital Logic Circuit Analysis and Design,感興趣的可以下載看看。

2015-11-03 18:19:09 0

0 定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)

2015-12-17 18:18:50 0

0 簡易交通燈控制邏輯電路設(shè)計(jì)_數(shù)字電子技術(shù)課程設(shè)計(jì)。

2022-03-22 11:59:33 265

265 數(shù)字邏輯電路第3章的PPT,一些難度大,質(zhì)量很高。

2016-06-03 16:57:53 0

0 數(shù)字電子鐘邏輯電路設(shè)計(jì),我自己編寫的,里面有橫多實(shí)用的東西

2016-06-22 16:12:01 54

54 VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(jì),感興趣的小伙伴們可以瞧一瞧。

2016-11-10 14:20:34 0

0 數(shù)字電子技術(shù)--時(shí)序邏輯電路

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)--組合邏輯電路

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)-- 組合邏輯電路

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)-- 時(shí)序邏輯電路

2016-12-12 21:54:28 0

0 分析數(shù)字邏輯電路的方法

2017-01-17 19:54:24 12

12 邏輯電路是包含邏輯關(guān)系的數(shù)字電路, 以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字離散信號(hào)的傳遞,邏輯運(yùn)算和操作的電路。最基本的邏輯電路是常見的門電路,而最簡單的門電路為與電路、或電路和非電路。

2017-05-22 09:58:43 20474

20474

數(shù)字信號(hào)與邏輯電路的認(rèn)識(shí)

2017-08-21 09:56:19 0

0 新型電子電路應(yīng)用指南 數(shù)字邏輯電路

2017-09-19 10:27:18 31

31 數(shù)字邏輯電路的用途和特點(diǎn) 數(shù)字電子電路中的后起之秀是數(shù)字邏輯電路。把它叫做數(shù)字電路是因?yàn)?b class="flag-6" style="color: red">電路中傳遞的雖然也是脈沖,但這些脈沖是用來表示- 二進(jìn)制數(shù)碼的,例如用高電平表示0。聲音圖像文字等信息經(jīng)過數(shù)字

2017-10-29 11:41:48 12

12 本文為大家?guī)砦宸N三人表決器電路設(shè)計(jì)方案,包括兩款仿真電路及程序分析,三款邏輯電路設(shè)計(jì)的原理詳解。

2018-01-17 18:49:21 298033

298033

組合邏輯電路的設(shè)計(jì)與分析過程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計(jì)步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 119435

119435

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。單一的與門、或門、與非門、或非門、非門等邏輯門不足以完成復(fù)雜的數(shù)字系統(tǒng)設(shè)計(jì)要求。組合邏輯電路是采用兩個(gè)或兩個(gè)以上基本邏輯門來實(shí)現(xiàn)更實(shí)用、復(fù)雜的邏輯功能。

2018-01-30 17:05:44 62959

62959

組合邏輯電路和時(shí)序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來的狀態(tài)無關(guān)。而時(shí)序邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出不僅取決于當(dāng)時(shí)的輸入信號(hào),而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2018-01-30 17:26:04 91327

91327

本文開始介紹了時(shí)序邏輯電路的特點(diǎn)和時(shí)序邏輯電路的三種邏輯器件,其次介紹了時(shí)序邏輯電路的組成與時(shí)序邏輯電路檢修方法,最后介紹了時(shí)序邏輯電路的應(yīng)用舉例。

2018-03-01 10:53:38 106881

106881

根據(jù)邏輯功能的不同,可把數(shù)字電路分為組合邏輯電路(Combinational Logic Circuit)和 時(shí)序邏輯電路(Sequential Logic Circuit)兩大類。

2018-07-20 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路基礎(chǔ)教程之時(shí)序邏輯電路的詳細(xì)資料概述。內(nèi)容包括了:1.時(shí)序邏輯電路分析2.若干常用時(shí)序邏輯電路3.時(shí)序邏輯電路設(shè)計(jì)

2018-10-17 08:00:00 0

0 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-02-26 15:22:20 30485

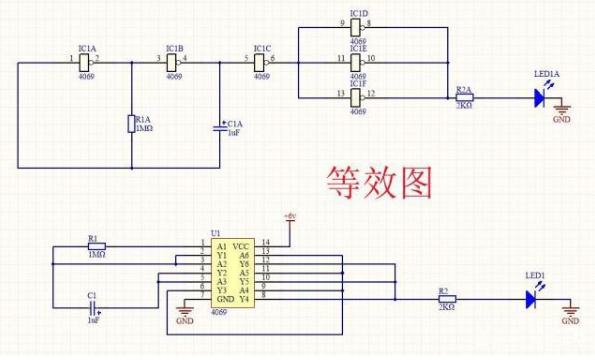

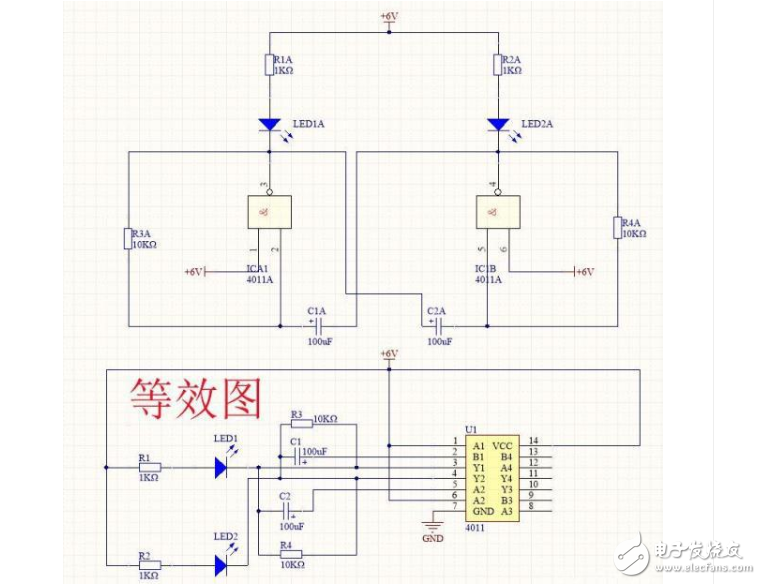

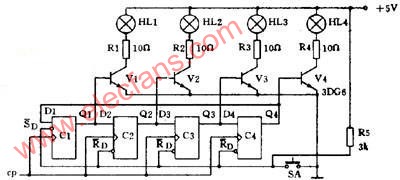

30485 本文章主要詳細(xì)介紹了數(shù)字邏輯電路應(yīng)用案例,分別是簡單防盜報(bào)警器、簡單車門報(bào)警、火警報(bào)警裝置、消防應(yīng)急燈。

2019-05-16 18:12:01 9551

9551

從整體上來看,數(shù)字邏輯電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類。在邏輯功能方面,組合邏輯電路在任一時(shí)刻的輸出信號(hào)僅與當(dāng)時(shí)的輸入信號(hào)有關(guān),與信號(hào)作用前電路原來所處的狀態(tài)無關(guān);而時(shí)序邏輯電路在任一時(shí)刻的輸出信號(hào)不僅與當(dāng)時(shí)的輸入信號(hào)有關(guān),而且還與電路原來的狀態(tài)有關(guān)。

2019-05-16 18:27:52 9581

9581

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-05-16 18:32:37 7636

7636

組合邏輯電路是無記憶數(shù)字邏輯電路,其任何時(shí)刻的輸出僅取決于其輸入的組合.

2019-06-22 10:53:20 46654

46654

在現(xiàn)階段,作為設(shè)計(jì)人員熟練掌握 Verilog HDL程序設(shè)計(jì)的多樣性和可綜合性,是至關(guān)重要的。作為數(shù)字集成電路的基礎(chǔ),基本數(shù)字邏輯電路的設(shè)計(jì)是進(jìn)行復(fù)雜電路的前提。本章通過對數(shù)字電路中基本邏輯電路的erilog HDL程序設(shè)計(jì)進(jìn)行講述,掌握基本邏輯電路的可綜合性設(shè)計(jì),為具有特定功能的復(fù)雜電路的設(shè)計(jì)打下基礎(chǔ)

2020-12-09 11:24:00 33

33 可規(guī)劃邏輯電路設(shè)計(jì)與實(shí)習(xí)報(bào)告

2021-12-23 17:28:52 5

5 避免常見的邏輯電路設(shè)計(jì)問題

2022-11-04 09:50:16 0

0 數(shù)字電路的分類

(1)按電路結(jié)構(gòu)分類

組合邏輯電路

時(shí)序邏輯電路:。

(2)按集成電路規(guī)模分:小規(guī)模、中規(guī)模和大規(guī)模。

2022-12-05 14:54:47 12

12 本文介紹開發(fā)組合邏輯電路時(shí)可能發(fā)生的意外開關(guān)事件,稱為危險(xiǎn)。 本文是關(guān)于使用邏輯門進(jìn)行組合電路設(shè)計(jì)和仿真的介紹性系列文章的第二部分。在上一篇文章中,我們介紹了 組合邏輯電路 以及如何簡化它們

2023-01-27 14:18:00 1078

1078

數(shù)字電路中的組合邏輯電路的設(shè)計(jì)與分析過程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計(jì)步驟,順便回顧一下組合邏輯電路的分析方法。

2023-02-03 09:56:23 2821

2821 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2023-03-14 17:06:50 4816

4816

時(shí)序電路的考察主要涉及分析與設(shè)計(jì)兩個(gè)部分,上文介紹了時(shí)序邏輯電路的一些分析方法,重點(diǎn)介紹了同步時(shí)序電路分析的步驟與注意事項(xiàng)。 本文就時(shí)序邏輯電路設(shè)計(jì)的相關(guān)問題進(jìn)行討論,重點(diǎn)介紹時(shí)序邏輯電路的核心部分——計(jì)數(shù)器。

2023-05-22 17:01:29 1882

1882

電子發(fā)燒友網(wǎng)站提供《MATLAB的數(shù)字邏輯電路Simulink仿真.pdf》資料免費(fèi)下載

2023-11-17 15:39:09 3

3 電子發(fā)燒友網(wǎng)站提供《Simulink數(shù)字邏輯電路的仿真.pdf》資料免費(fèi)下載

2023-11-18 09:24:08 4

4 當(dāng)邏輯電路由多個(gè)邏輯門組成且不含存儲(chǔ)電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合邏輯電路。

2024-02-04 11:46:36 320

320

組合邏輯電路和時(shí)序邏輯電路是數(shù)字電路中兩種重要的邏輯電路類型,它們主要區(qū)別在于其輸出信號(hào)的依賴關(guān)系和對時(shí)間的敏感性。

2024-02-04 16:00:27 449

449 時(shí)序邏輯電路是一種能夠存儲(chǔ)信息并根據(jù)時(shí)鐘信號(hào)按照特定順序執(zhí)行操作的電路。它是計(jì)算機(jī)硬件中非常重要的一部分,用于實(shí)現(xiàn)存儲(chǔ)器、時(shí)序控制器等功能。與之相對的是組合邏輯電路,它根據(jù)輸入信號(hào)的組合情況,立即

2024-02-06 11:18:34 499

499

電子發(fā)燒友App

電子發(fā)燒友App

評論